| Die letzten 6 Beiträge |

| deppensido |

nochmals danke für die Erläuterung. Die Zeit für die Leitungen wird bei uns nicht berücksichtigt, daher würde ich in so einem Fall raten müssen, aber da Verzögerungszeiten immer vorgegeben werden, wird es eindeutig bleiben. Brauch mir also darüber keine Sorgen machen. Ich war mir bei dem FlipFlop jetzt auch nicht sicher, ob bei der steigenden Flanke für b und z, das Signal noch 1 oder bereits 0 ist. Hab da einfach mal 0 angenommen. Aber ansonsten hab ich es wohl verstanden, vielen dank nochmals dafür.

Grüße |

| eulerscheZahl |

Neben der Verzögerungszeit des Bauteils (verspätete Ausgabe) gibt es noch die setup-time: das Eingangssignal muss bereits kurz vor der Taktflanke anliegen.

Ich ignoriere das jetzt einfach mal, dann:

Das Latch passt so, wie du es gezeichnet hast.

Beim Flipflop kann man streiten, was zuerst da ist, clock oder Eingang, hier gewinnt dann die kürzere Leitung. Wenn die des Dateneingangs kürzer ist, passt deine Zeichnung so, wenn die clock schneller ist, hast du eine Treppenform, ähnlich wie oben, nur alles um ein Kästchen nach links verschoben. |

| deppensido |

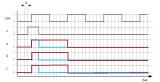

um zu testen, ob ich es richtig verstanden habe, habe ich das Zeitdiagramm gezeichnet für den Fall, dass das Latch keine Verzögerungszeit hat. Stimmt das so? Blau ist für das D-Latch, Dunkelrot für das Flipflop.

Grüße

deppensido hat dieses Bild (verkleinerte Version) angehängt:

|

| deppensido |

danke für die Antwort. Ich denke, ich verstehe jetzt, wie die Signale zustande kommen. Ist ja eigentlich doch ganz einfach...

Grüße, Volker |

| eulerscheZahl |

Zum Flipflop: es gibt welche, die nur bei positiver/negativer Flanke den Zustand übernehmen und welche, die es bei beidem tun. In der Aufgabe hast du eines, das auf die positive Taktflanke gesteuert ist.

Ich habe die Bilder mal etwas nachbearbeitet, wird es jetzt klar?

Falls nicht, einfach nochmal fragen

eulerscheZahl hat dieses Bild (verkleinerte Version) angehängt:

|

| deppensido |

Zeitdiagramme zu einem Schieberegister

Hallo,

im Anhang sind die Aufgaben und Lösungen zu meinem Problem zu finden.

Mein Problem: Ich kann die Zeitdiagramme überhaupt nicht nachvollziehen, ich weiß nur, dass ein D-Latch jederzeit den Ausgang Zustandsgesteuert ausgeben kann und das D-FlipFlop den Ausgang Flankengesteuert ausgibt, also beim Wechsel von CLK von 0 auf 1 und umgekehrt.

Ich versteh aber gar nicht, wann die Zeitdiagramme von 0 auf 1 springen und wie lange diese dann 1 sind. In meiner dazugehörigen Übung wurde die Aufgabe leider nicht besprochen und die Musterlösung gibt ja einfach nur die Lösung ohne Erklärung an.

Ich hoffe mir kann jemand weiterhelfen, bin langsam am verzweifeln. Vielen Dank im voraus.

Grüße, Volker

deppensido hat diese Bilder (verkleinerte Versionen) angehängt:

|

|

|