RAM: Adressbus und Addierwerk RAM: Adressbus und Addierwerk |

Rivenü

unregistriert

|

|

| RAM: Adressbus und Addierwerk |

|

Meine Frage:

So Leute, ich habe folgende Aufgabe bekommen: Gebt bitte zu jedem Aufgabenteil den genauen Rechenweg an.

In einem Rechner sind 4GB RAM (Arbeitsspeicher) verbaut.

1. Wieviele Binary Cells und wieviele RS-Flip-Flops werden benötigt um diesen Speicher zu realisieren?

2. In heute üblichen Systemen ist der RAM als Tabellenspeicher mit 64bit Wortbreite realisiert. Wieso

braucht man nicht für jede Zeile des Tabellenspeichers eine eigene Adressleitung?

3. Wieviele Leitungen muss der Adressbus zu diesem Speicher mindestens haben, um jede Zeile ansprechen

zu können?

Zum Rechenwerk:

1. Ein Addierwerk soll zwei 32Bit-Zahlen addieren. Wieviele Halbaddierer müssen für diese Rechenoperation

in dem Addierwerk vorhanden sein?

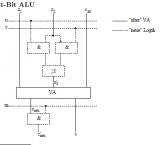

2. Wie kann man mit einer ALU eine Binärzahl von einer anderen subtrahieren? Gebe bitte die Belegung der

Steuerleitungen an und erkläre in Stichpunkten warum dadurch die ALU eine Subtraktion durchführt.

Meine Ideen:

Also ich hab von 4 Aufgaben nur die nicht hinbekommen, manches verwirrt mich.

1. Eine Binary Cell kann 1 Bit speichern. 4 GB werden realisiert, sprich ich muss 4 GB in Bit umrechnen? Das wären nach der Standardisierung 32 000 000 000 Bit und damit auch Binary Cells?

2. Hab ich keinen Schimmer, ich gehe davon aus, dass das etwas mit den Multi-, und Demultiplexern zutun hat?

3. Ebenso wenig Ahnung, ich schätze 16, wenn man mit 1 zu 4 Demulti- und Multiplexern arbeitet?

----

1. Zum addieren von n-Zahlen benötigt man eig. Volladdierer wegen dem Übertrag (Carry-bit). Sprich man benötig n-1 Volladdierer und einen Halbaddierer, da für die niederwertigste Stelle kein Übertrag besteht. Also brauche ich 31*2+1=63 Halbaddierer?

2. Belegung der Steuerleitungen: In dem Fall m auf 1, v auf 1 und u auf 0. Das ganze wird doch dann subtrahiert, weil bei z2 dann über das AND ne Invertierung erfolgt oder?

Rivenü hat diese Bilder (verkleinerte Versionen) angehängt:

|

|

31.10.2015 22:47

31.10.2015 22:47 |

|

|

|

|

1.2) Der hast 64bit Busbreite, kannst dir also alle 8 Byte auf einmal holen.

1.3) 4GB = 2^32 Byte. Das heißt, du brauchst 32 Bit für die Addressleitung, um jedes Byte einzeln zu adressieren. Aber da du immer 2^6 Byte auf einmal holst, reichen 32-6 = 26 Bit Adressleitung.

2.2) Belegung passt, den Übertrag solltest du nach Tabelle noch setzen.

__________________

Syntax Highlighting fürs Board (Link)

|

|

01.11.2015 07:27

01.11.2015 07:27 |

|

|

RivenüsVerehrer

unregistriert

|

|

| RE: RAM: Adressbus und Addierwerk |

|

Hi Rivenü,

Hast du eventuell die Lösungen zu deinen Aufgaben?

Das würde mir sehr helfen, da ich dieselben Aufgaben bekommen habe.

LG

|

|

20.12.2021 13:23

20.12.2021 13:23 |

|

|

|